JEDEC releases new LPDDR6 Standard that offers enhanced performance, power efficiency and security

JEDEC Solid State Technology Association recently announced the publication of JESD209-6, the latest Low Power Double Data Rate 6 (LPDDR6) standard. This is designed to significantly boost memory speed and efficiency for a variety of uses, including mobile devices and AI.

For enabling AI applications and other high-performance workloads, LPDDR6 employs a dual sub-channel architecture that allows for flexible operation while maintaining a small access granularity of 32 bytes.

Let’s take a look at the key features of the LPDDR6 Standard

High performance

- 2 sub-channels per die, 12 data signal lines (DQs) per sub-channel to optimize channel performance capabilities

- Each sub-channel includes 4 command/address (CA) signals, optimized to reduce ball count and improve data access speed

- Static efficiency mode is designed to support high-capacity memory configurations and maximize bank resource utilization

- Flexible data access, on-the-fly burst length control to support 32B & 64B access

- Dynamic write NT-ODT (non-target on-die termination) enables the memory to adjust ODT based on workload demands, improving signal integrity

Power Efficiency

- LPDDR6 operates with a lower voltage and low power consumption capable VDD2 supply as compared to LPDDR5, and mandates two supplies for VDD2

- Alternating clock command inputs are used to enhance performance and efficiency

- Dynamic Voltage Frequency Scaling for Low Power (DVFSL) lowers the VDD2 supply during low-frequency operation to reduce power consumption

- Dynamic Efficiency mode utilizes a single sub-channel interface for low-power, low-bandwidth use cases

- Support for both partial self and active refresh to reduce refresh power usage

Security and Reliability

- Per Row Activation Counting (PRAC) to support DRAM data integrity

- Carve-out Meta mode is defined to enhance overall system reliability by allocating specific memory regions for critical tasks

- Support for programmable link protection scheme and on-die error correction code (ECC)

- Capable of supporting Command/Address (CA) parity, error scrubbing, and memory built-in self-test (MBIST) for enhanced error detection and system reliability

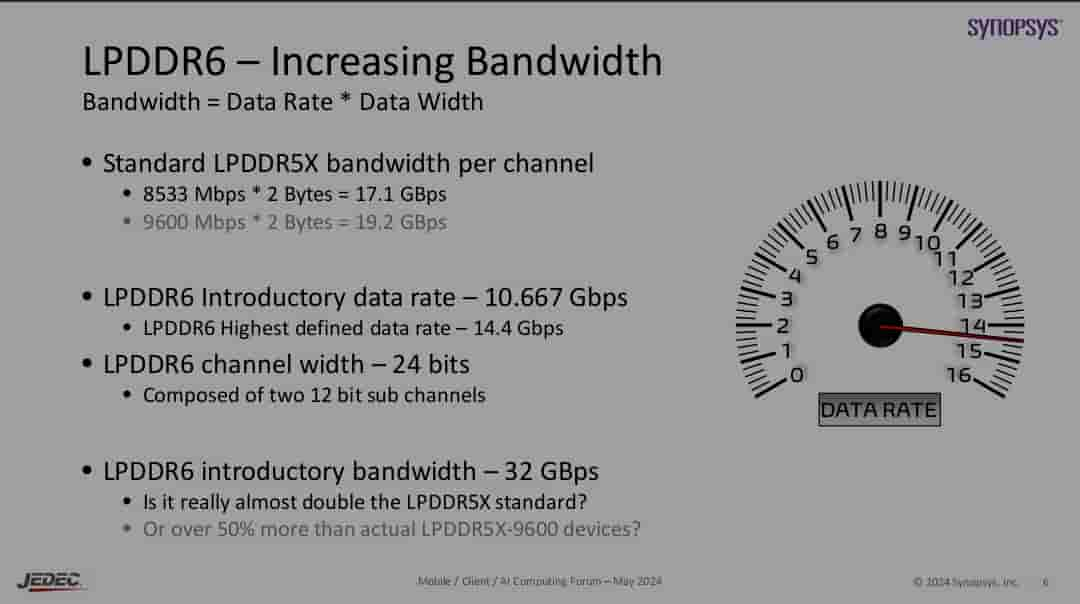

Previously in its presentation, the company revealed that LPDDR6 may offer a 14.4Gbps highest defined data rate, and introductory bandwidth will be 32Gbps. Development plans for LPDDR6 included a focus on increasing bandwidth, lowering power usage and enhanced RAS.

It is expected that LPDDR6-based memory products will make their debut in late 2025. However, we should wait for official confirmation to know the details.